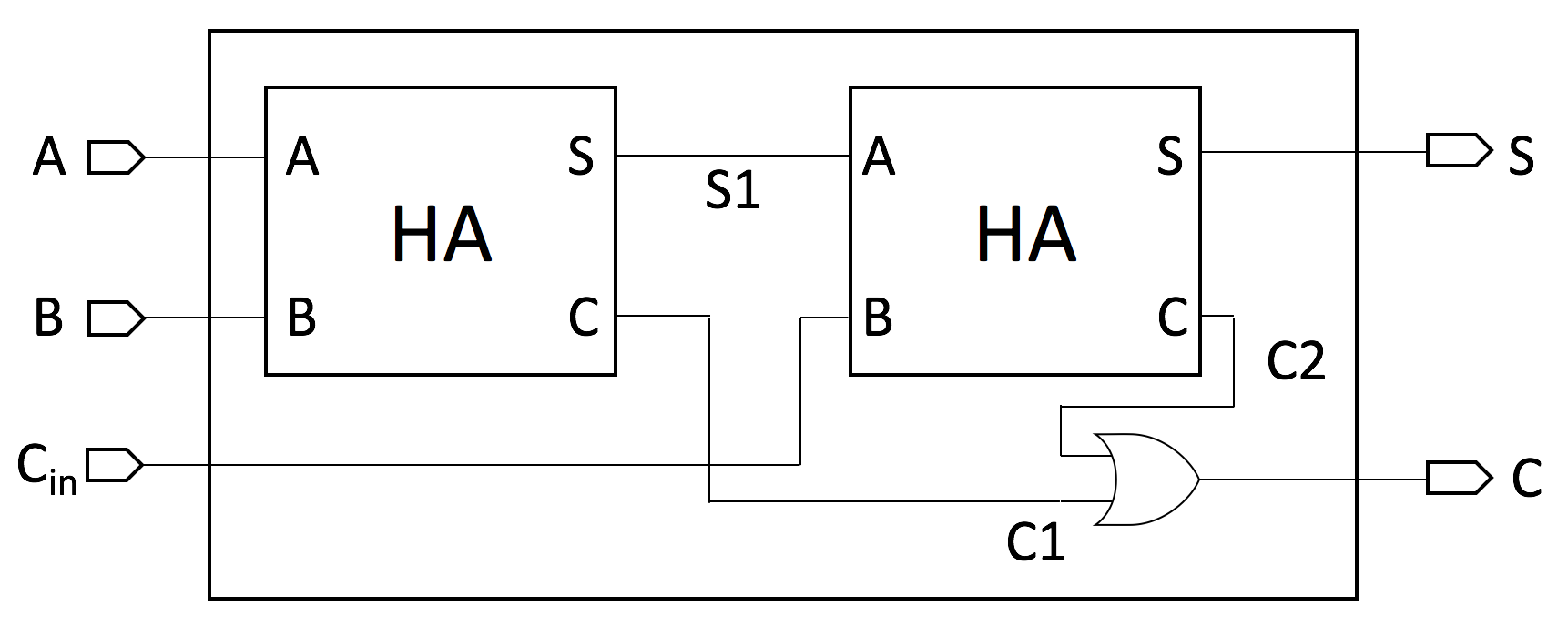

Design and Explain Full Adder by Using Vhdl

VHDL code for Full adder using half adder with testbench

VHDL code for Full adder using half adder

half_adder.vhdl

ENTITY half_adder IS --- Half Adder PORT(A,B: IN BIT ; S, Cout : OUT BIT); END full_adder; ARCHITECTURE half_adder_beh OF half_adder IS BEGIN S <= A xor B; Cout <= A and B; END full_adder_beh; or_gate.vhdl

ENTITY or_gate IS PORT(A,B: IN BIT ; C : OUT BIT); END or_gate; ARCHITECTURE or_gate_beh OF or_gate IS BEGIN C <= A or B; END or_gate_beh; full_adder.vhdl

ENTITY full_adder IS --- Full Adder PORT(A,B,Cin: IN BIT ; S, C : OUT BIT); END full_adder; ARCHITECTURE str OF full_adder IS --component Declaration Component half_adder IS PORT(A,B: IN BIT ; S, Cout : OUT BIT); END Component; Component or_gate IS PORT(A,B: IN BIT ; C : OUT BIT); END Component; signal s1,c2,c3:std_logic; BEGIN X1: half_adder port map(A,B,s1,c1); X2: half_adder port map(s1,Cin,S,c2); X3: or_gate port map(c1,c2,C); END str; testbench

LIBRARY ieee; USE ieee.std_logic_1164.ALL; ENTITY Testbench_full_adder IS END Testbench_full_adder; ARCHITECTURE behavior OF Testbench_full_adder IS -- Component Declaration for the Unit Under Test (UUT) COMPONENT full_adder PORT( A : IN std_logic; B : IN std_logic; Cin : IN std_logic; S : OUT std_logic; C : OUT std_logic ); END COMPONENT; --Inputs signal A : std_logic := '0'; signal B : std_logic := '0'; signal Cin : std_logic := '0'; --Outputs signal S : std_logic; signal C : std_logic; BEGIN -- Instantiate the Unit Under Test (UUT) uut: full_adder PORT MAP ( A => A, B => B, Cin => Cin, S => S, C => C ); -- Stimulus process stim_proc: process begin -- hold reset state for 100 ns. wait for 100 ns; -- insert stimulus here A <= '1'; B <= '0'; Cin <= '0'; wait for 10 ns; A <= '0'; B <= '1'; Cin <= '0'; wait for 10 ns; A <= '1'; B <= '1'; Cin <= '0'; wait for 10 ns; A <= '0'; B <= '0'; Cin <= '1'; wait for 10 ns; A <= '1'; B <= '0'; Cin <= '1'; wait for 10 ns; A <= '0'; B <= '1'; Cin <= '1'; wait for 10 ns; A <= '1'; B <= '1'; Cin <= '1'; wait for 10 ns; end process; END; Popular posts from this blog

VHDL Code for AND gate With Test Bench

VHDL Code for AND gate With Test Bench li brary IEEE; use IEEE.std_logic_1164.all; entity andgate is Port( A : in std_logic; B : in std_logic; Y : out std_logic ); end andgate; architecture Behavioral of andgate is begin Y<= A and B ; end Behavioral; Test Bench library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity and_tb is -- Port ( ); end and_tb; architecture Behavioral of and_tb is --Component name and entity's name must be same --ports must be same component andgate is Port (A,B:in std_logic; C: out std_logic ); end component; --inputs signal a: std_logic:= '0'; signal b: std_logic:= '0'; --outputs signal c : std_logic; begin uut: andgate PORT MAP(a=>A,b=>B,c=>C); --Stimulus Process stim_proc:process begin wait for 10ns; a<='1'; b<='0'; wait for 10ns; a<='0'; b<='1'; wait for 10ns; a<='0'; b<='0'; wait for 10ns; a<='

VHDL code for Full Adder With Test bench

VHDL code for Full Adder With Test bench The full - adder circuit adds three one-bit binary numbers (C A B) and outputs two one-bit binary numbers, a sum (S) and a carry (C1). The full - adder is usually a component in a cascade of adders , which add 8, 16, 32, etc. binary numbers. ENTITY full_adder IS --- Full Adder PORT(A,B,Cin: IN BIT ; S, Cout : OUT BIT); END full_adder; ARCHITECTURE full_adder_beh OF full_adder IS BEGIN PROCESS(A,B,Cin) -- Sensitive on all the three bits VARIABLE temp :BIT; BEGIN --- DOES the addition in one DELTA time temp := A XOR B; S <= temp XOR Cin; Cout <= (A AND B) OR (temp AND Cin); END PROCESS ; END full_adder_beh; Test Bench LIBRARY ieee; USE ieee.std_logic_1164.ALL; ENTITY Testbench_full_adder IS END Testbench_full_adder; ARCHITECTURE behavior OF Testbench_full_adder IS -- Component Declaration for the

Design and Explain Full Adder by Using Vhdl

Source: https://techyelf.blogspot.com/2017/09/vhdl-code-for-full-adder-using-half.html

0 Response to "Design and Explain Full Adder by Using Vhdl"

Postar um comentário